# Dissertation

# submitted to the

Combined Faculties of the Natural Sciences and Mathematics of the Ruperto-Carola-University of Heidelberg, Germany for the degree of

**Doctor of Natural Sciences**

Put forward by

Wei Shen

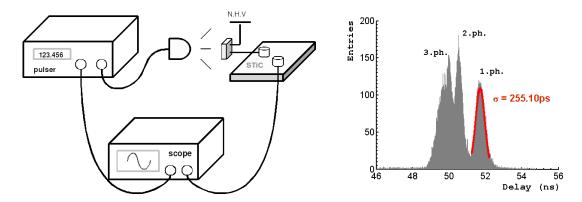

born in: Zhejiang, China

Oral Examination: 24.07.2012

# Development of High Performance Readout ASICs for Silicon Photomultipliers (SiPMs)

Referees: Prof. Dr. Hans-Christian Schultz-Coulon

Prof. Dr. Peter Fischer

#### Abstract

Silicon Photomultipliers (SiPMs) are novel kind of solid state photon detectors with extremely high photon detection resolution. They are composed of hundreds or thousands of avalanche photon diode pixels connected in parallel. These avalanche photon diodes are operated in Geiger Mode. SiPMs have the same magnitude of multiplication gain compared to the conventional photomultipliers (PMTs). Moreover, they have a lot of advantages such as compactness, relatively low bias voltage and magnetic field immunity etc. Special readout electronics are required to preserve the high performance of the detector. KLauS and STiC are two CMOS ASIC chips designed in particular for SiPMs. KLauS is used for SiPM charge readout applications. Since SiPMs have a much larger detector capacitance compared to other solid state photon detectors such as PIN diodes and APDs, a few special techniques are used inside the chip to make sure a descent signal to noise ratio for pixel charge signal can be obtained. STiC is a chip dedicated to SiPM time-of-flight applications. High bandwidth and low jitter design schemes are mandatory for such applications where time jitter less than tens of picosends is required. Design schemes and error analysis as well as measurement results are presented in the thesis.

## Zusammenfassung

Silizium-Photomultiplier (SiPMs) sind neuartige Solid-State-Photonen-Detektoren mit extrem hoher Photonendetektionsauflösung. Sie werden von Hunderten oder Tausenden parallel verbundene Avalanche-Photonen Diodenpixel ausgemacht, die in Geiger-Mode betrieben sind. SiPMs haben gleichen Multiplikationsverstärkung im Vergleich zu den Photomultiplier (PMT). Auerdem haben sie viele Vorteile wie Kompaktheit, relativ niedrigen Vorspannung und Magnetfeld immun usw. Spezielle Auslese-Elektronik sind erforderlich, um die hohe Leistungsfähigkeit des Detektors zu bewahren. KLauS und STiC sind zwei CMOS-ASIC-Chips insbesondere für SiPMs entwickelt. KLauS ist für SiPM Ladungsauslese eingesetzt. Weil SiPMs eine viel gröere Kapazität haben im Vergleich zu anderen Festkörper-Photonen-Detektoren, wie PIN-Dioden und APDs, werden einige spezielle Techniken innerhalb des Chips verwendet, um ein hohes Signal-Rausch-Verhältnis für Pixelladung Signal zu erhalten. STiC ist ein Chip, der fü SiPM Time-of-Flight-Anwendungen entwickelt wird. Hohe Bandbreite und geringem Jitter Design Systeme sind obligatorisch für solche Anwendungen, bei denen Time-Jitter von weniger als zehn picosends erforderlich ist. Design-Schema und Fehleranalyse sowie Mess-Ergebnisse sind in der Arbeit vorgestellt.

# Contents

| C | onter | its                   |                                                       |    |

|---|-------|-----------------------|-------------------------------------------------------|----|

| 1 | Intr  | oduct                 | on                                                    | 1  |

|   | 1.1   | Introd                | uction to Silicon Photomultipliers (SiPMs)            | 1  |

|   | 1.2   | Main                  | Specifications of SiPMs                               | ę  |

|   | 1.3   | Outlin                | e of the Thesis                                       | E  |

| 2 | Silio | con Ph                | otomultipliers - Structures and Physics               | 7  |

|   | 2.1   | $\operatorname{SiPM}$ | Development Overview                                  | 7  |

|   | 2.2   | Key P                 | pints in Silicon Photomultiplier Design               | 13 |

|   |       | 2.2.1                 | Avalanche Junction with Reach Through Structure (RTS) | 13 |

|   |       | 2.2.2                 | Pre-mature Breakdown (PEB) Prevention                 | 14 |

|   |       | 2.2.3                 | Quench Circuits                                       | 16 |

|   |       |                       | 2.2.3.1 Passive Quench Circuit (PQC)                  | 16 |

|   |       |                       | 2.2.3.2 Active Quench Circuit (AQC)                   | 17 |

|   | 2.3   | Perfor                | mance of Silicon Photomultipliers                     | 18 |

|   |       | 2.3.1                 | Breakdown Voltage and Temperature Dependence          | 18 |

|   |       | 2.3.2                 | Dynamic Range and Saturation Effects                  | 20 |

|   |       | 2.3.3                 | Dark Noise                                            | 22 |

|   |       | 2.3.4                 | After-pulse Effect                                    | 24 |

|   |       | 2.3.5                 | Optical Crosstalk                                     | 26 |

|   |       | 2.3.6                 | Photon Detection Efficiency (PDE)                     | 27 |

|   | 2.4   | Electr                | cal Model for Silicon Photomultipliers                | 29 |

|   |       | 2.4.1                 | Electrical Model and Parameter Mesurements            | 30 |

|   |       | 2.4.2                 | Waveform Analysis and Model Simplification            | 31 |

| 3 | Bas   | ics on                | Analog Signal Processing and Noise Analysis           | 35 |

|   | 3.1   | Signal                | Processing using the Laplace Transform                | 35 |

|   | 3.2   | Poles                 | and Zeros in the Laplace Transform                    | 41 |

|   | 3 3   | Noise                 | Δ nalveje                                             | 15 |

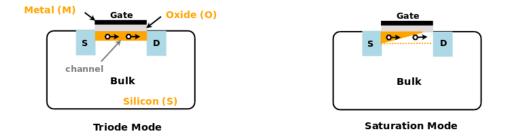

|   | 3.4   | MOS     | Transistor Model and Noise Sources                                                                                                                                            |

|---|-------|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|   |       | 3.4.1   | MOS Transistor Model                                                                                                                                                          |

|   |       | 3.4.2   | Noise Sources in MOS Transistors                                                                                                                                              |

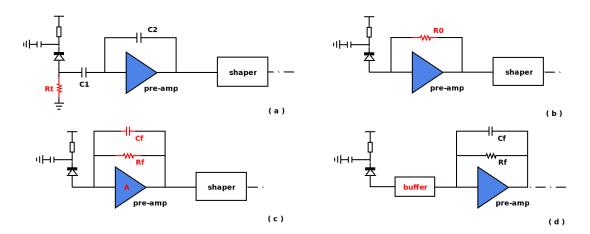

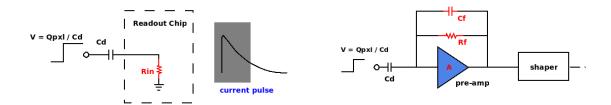

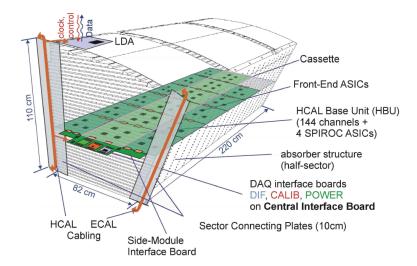

| 4 | Cha   | arge Se | ensitive Readout ASIC For Silicon Photomultipliers 47                                                                                                                         |

|   | 4.1   | Pixel-  | SNR and Non-uniformity                                                                                                                                                        |

|   | 4.2   | Detect  | tor Leakage Current                                                                                                                                                           |

|   | 4.3   | Dark    | Noise Pile-up with After-pulse and Crosstalk Effects                                                                                                                          |

|   | 4.4   | Comp    | arison of Different Readout Schemes                                                                                                                                           |

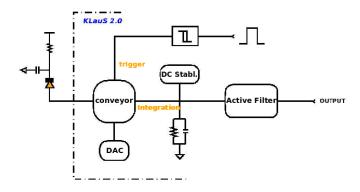

|   | 4.5   | KLaus   | S - Kanäle zur Ladungsauslese für Silicon Photomultiplier $\dots \dots \dots$ |

|   |       | 4.5.1   | Chip Overview                                                                                                                                                                 |

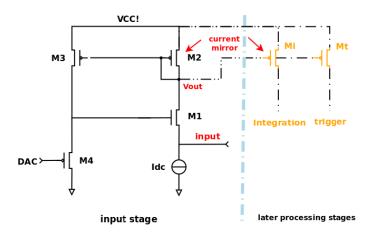

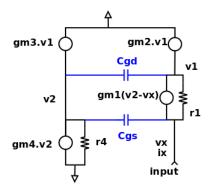

|   |       | 4.5.2   | Input Stage (Current Conveyor)                                                                                                                                                |

|   |       |         | 4.5.2.1 Low Frequency (LF) Response                                                                                                                                           |

|   |       |         | 4.5.2.2 High Frequency (HF) Response                                                                                                                                          |

|   |       |         | 4.5.2.3 Stability                                                                                                                                                             |

|   |       |         | 4.5.2.4 Input Bias Tuning Voltage                                                                                                                                             |

|   |       |         | 4.5.2.5 Noise                                                                                                                                                                 |

|   |       | 4.5.3   | Low Power DAC                                                                                                                                                                 |

|   |       |         | 4.5.3.1 DAC Structure                                                                                                                                                         |

|   |       |         | 4.5.3.2 Mismatch and Non-linearity 67                                                                                                                                         |

|   |       | 4.5.4   | Shaping and Pedestal Stabilization                                                                                                                                            |

|   |       | 4.5.5   | Charge Collection Efficiency                                                                                                                                                  |

|   |       | 4.5.6   | Noise Performance                                                                                                                                                             |

|   |       | 4.5.7   | Power Pulsing                                                                                                                                                                 |

| 5 | Silio | con Ph  | otomultiplier Fast Timing Readout 83                                                                                                                                          |

|   | 5.1   | Detect  | for Intrinsic Timing Resolution                                                                                                                                               |

|   |       | 5.1.1   | Single Photon Timing Response                                                                                                                                                 |

|   |       | 5.1.2   | Parasitic Effects                                                                                                                                                             |

|   |       | 5.1.3   | Pile-up Effects                                                                                                                                                               |

|   |       | 5.1.4   | Pixel Uniformity                                                                                                                                                              |

|   |       | 5.1.5   | Passive Quench Resistor Noise                                                                                                                                                 |

|   | 5.2   | STiC    | - Silicon Photomultiplier Timing Chip                                                                                                                                         |

|   |       | 5.2.1   | Input Stage                                                                                                                                                                   |

|   |       | 5.2.2   | Noise and Time Jitter                                                                                                                                                         |

|   |       | 5.2.3   | Current Discriminator                                                                                                                                                         |

|   |       | 5.2.4   | Compensation and Threshold Circuit                                                                                                                                            |

|   |       | 5.2.5   | Charge Encoding using the Time over Threshold (ToT) method                                                                                                                    |

|   |       | 5.2.6   | Hit Logic Processing                                                                                                                                                          |

# CONTENTS

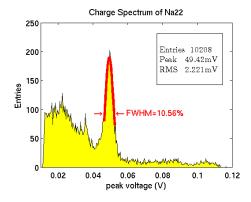

| 6                         | Measurement Results |                    |     |  |  |

|---------------------------|---------------------|--------------------|-----|--|--|

|                           | 6.1                 | KLauS Measurements | 121 |  |  |

|                           | 6.2                 | STiC Measurements  | 126 |  |  |

| 7                         | Sun                 | nmary              | 131 |  |  |

| $\mathbf{R}^{\epsilon}$   | efere               | nces               | 133 |  |  |

| $\mathbf{A}_{]}$          | ppen                | dix A              | 143 |  |  |

| $\mathbf{A}_{\mathbf{j}}$ | open                | dix B              | 145 |  |  |

# Chapter 1

# Introduction

Silicon Photomultipliers (SiPMs) are novel kind of silicon photon detectors. They have several advantages over conventional photomultipliers such as small size and insensitivity to magnetic fields. Moreover, their excellent photon resolving capabilities and timing performance make them a better solid state photon detector than avalanche photodiodes (APDs). In this chapter, the basic operation principle of SiPMs and their main characteristic specifications will be introduced.

## 1.1 Introduction to Silicon Photomultipliers (SiPMs)

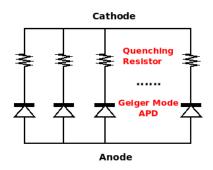

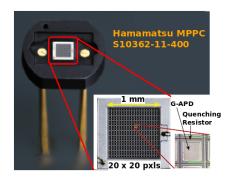

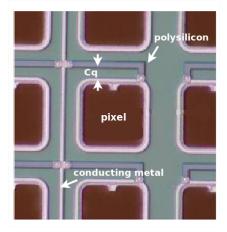

A silicon photomultiplier device is a silicon pixel array which is composed of hundreds of identical pixels. Each pixel consists of an avalanche photodiode (APD) and an quenching resistor in series as illustrated in Figure 1.1. The APDs are biased above the breakdown voltage and thus operated in the so-called Geiger mode, in which the avalanche multiplication process cannot be stopped automatically. The quenching resistor provides a local negative feedback to the pixel diode. The large avalanche current will cause a significant voltage drop on the resistor thus reducing the total bias voltage across the resistor. Once it goes back to the breakdown voltage, the avalanche will be quenched; the pixel will then recover to the initial state and be ready for another avalanche process. The device usually has a surface size of several mm<sup>2</sup> and the pixel to pixel distance (pitch) is normally tens of microns. Figure 1.2 shows a picture of a typical SiPM product from Hamamatsu, Japan [1]. The polysilicon quenching resistor can be clearly seen on the picture; it is usually fabricated on top of the silicon die and close

Fig. 1.1: Sketch of a SiPM pixel array

Fig. 1.2: Photo of Hamamatsu MPPC [1].

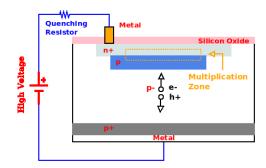

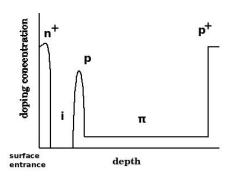

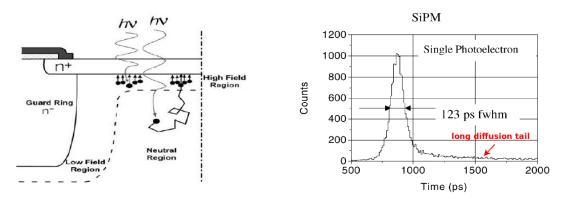

Fig. 1.3: Typical APD doping profile

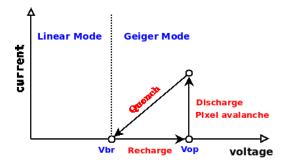

Fig. 1.4: SiPM pixel operating sketch

to the edge of the APD senstive area. More details about the detector structures will be described in Chapter 2.

Figure 1.3 shows a typical doping profile of an APD pixel. An  $n^+$ -p-p<sup>-</sup>-p<sup>+</sup> (or reverse type p<sup>+</sup>-n- $n^-$ -n<sup>+</sup>) structure is formed. The diode junction is formed by  $n^+$  on p doping, which has a very high electric field inside and is indicated as multiplication zone in the figure. Once the photon penetrates the detector surface, an electron hole pair will be generated inside the pixel volume. The generated carriers will drift to the multiplication zone and then trigger the Geiger mode avalanche process. The trigger and quench process can be explained by the sketch in Figure 1.4. Before triggering, the APD is biased at  $V_{op}$  in the Geiger mode operation region which is several volts above the breakdown voltage  $V_{br}$ . Once photon generated carrier triggers an avalanche event, the current inside the APD will be increased rapidly by the carrier multiplication; the current flowing through the quenching resistor then brings down the APD voltage back to  $V_{br}$  and stops the multiplication process. A more comprehensive detector signal analysis can be found in Chapter 2 section 2.4.2.

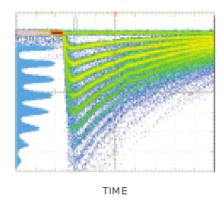

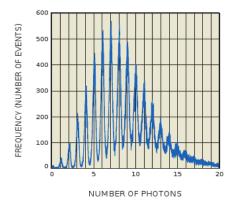

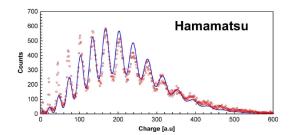

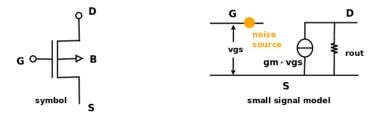

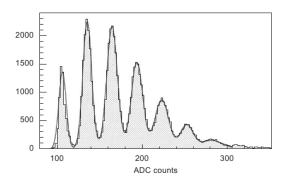

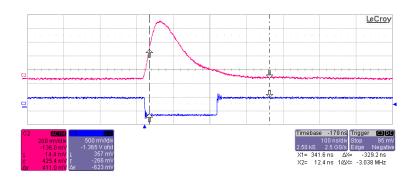

Due to the nature of the Geiger mode avalanche, each single pixel can be used as a binary photon counter. The output signal of the pixel is always identical no matter how many photons are absorbed by the APD. Since the pixels are connected in parallel, the SiPM detector can be used as a photon counting device, if the photon number is much smaller than the pixel number and the light is spread over the whole device. Figure 1.5 shows an oscilloscope snapshot of the SiPM output waveform. The displayed waveforms correspond to signals of one, two, ... pixels fired at the same time. If this output signal charge is integrated, it should yield a charge spectrum like the one shown in Figure 1.6. Here,

Fig. 1.5: SiPM output waveforms [1]

Fig. 1.6: Typical SiPM photon spectrum [1]

the x-axis shows the amount of charge (or number of photons) detected and the y-axis is the number of recorded events. SiPM devices are proven to have a very high photon detection resolution and thus quite efficient in photon counting. Therefore, SiPMs became relative popular in applications where an exact information about photon number is desired. In addition, the large current signal due to the Geiger mode avalanche leads to a very fast signal rise and promises a low timing uncertainty which typically is in the sub-nano second range. Consequently, SiPMs are attractive photon detector candidates for applications with precise timing pick-ups such as Time-of-Flight (ToF) measurements.

## 1.2 Main Specifications of SiPMs

The most important specifications of SiPMs are the **gain**, **dark noise**, **crosstalk** and **afterpulse** as well as the **photon detection efficiency (PDE)**.

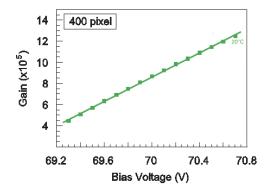

Gain. The gain of the avalanche is defined as the ratio of the final multiplicated carrier number after charge multiplication to the incident number of carriers. Since the photodiodes are operated in Geiger mode, the output carrier number is always the same no matter how many carriers trigger the process. Therefore, the incident carrier number is assumed to be one and the gain equals to the final output carrier number. The gain times the eletron charge is the pixel output charge, which can be measured by the distance between two neighbouring peaks in Figure 1.6. The pixel charge approximately equals to  $V_{ov} \cdot C_{pxl}$  ( $V_{ov}$  is called overvoltage, it equals to  $V_{op} - V_{br}$ ;  $C_{pxl}$  is the APD diode capacitance). This can be explained by looking at the charge stored by the APD before and after the avalanche which is  $V_{op} \cdot C_{pxl}$  and  $V_{br} \cdot C_{pxl}$  as shown in Figure 1.4. The gain measurement of the device shown in Figure 1.2 is displayed in Figure 1.7 [2]. The linearity of the plot can be explained by the relation above. However, the avalanche and quenching process are generally more complicated, such that the exact expression for the pixel gain has two more terms in addition to  $V_{ov} \cdot C_{pxl}$ . Details can be found in Chapter 2 section 2.4.2.

**Dark Noise.** Similar to the photon generated carriers, thermally irritated electron hole pairs can also trigger Geiger pulses. These thermal pulses exist at all times since electron-hole generation and recombination are continious processes under all temperature conditions even if the device is put in a dark environment without any photon. These pulses are called **dark noise**. They are considered to be

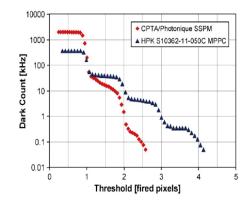

Fig. 1.7: Gain measurement vs. bias voltage [2] Fig. 1.8: Dark noise rate vs. threshold value [3]

a noise source because they are indistinguishable from normal photon induced pulses. Normally, the dark noise can be largely reduced statistically if the incoming photon signal has a certain correlation with some physical trigger signal. However, if the dark noise rate is too high, the output pulse will pile up and the pedestal of the output terminal will be shifted and fluctuate with some uncertainty. This will degrade the signal quality of the real photon signal. Details about the origin of the dark noise will be discussed in Chapter 2 section 2.4.2. And the degradation due to pile-up effects will be examined in Chapter 4 section 4.3.

Crosstalk. The dark noise also includes pulses corresponding to more than one pixel charge, which from a pure statistical point of view should be nearly impossible. The reason for this phenomenon is that the avalanche process can be propogated to the surroundings with the assistance of the crosstalk effect. During avalanching photons can be generated from the mulplication process. These photons penetrate into neighbouring pixels and trigger an avalanche there; the output pulse then is the combination of all the pixels signals. Simple measurement can be carried out to quantize the crosstalk probability. A discrminator with tunable thresholds can be used to measure the dark noise rate. By setting the threshold to different values, the dark noise rate for multiple photons can be measured as shown in Figure 1.8 [3] (results for two different SiPMs). The curve is similar to a step function. The ratio between different steps can be used to determined the crosstalk probability. More details about the crosstalk effect can be found in Chapter 2 section 2.3.5.

Afterpulse. Afterpulse is another drawback of SiPMs and usually refers to correlated pulses initiated by trapped electrons after the original avalanche, i.e. pulses are caused by charge carriers which are first captured during the avalanche by the trapping centers inside the junction area. Although they are also indistinguishable from a real photon signal, their properties can be investigated by studying the timing durations of two successive dark noise pulses. The release time of the captured carriers follows an exponential probability function, whose time constant can be determined by the measurement, which will be discussed in Chapter 2 section 2.3.4.

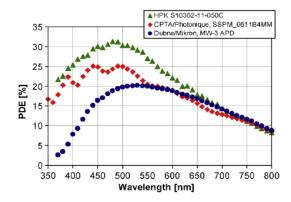

**Photon Detection Efficiency (PDE).** The probability for a photon to trigger an avalanche process is defined as **photon detection efficiency**. It is a very important quantity for any photon sensor and it determines how large the loss of photon is not seen by the whole photon detection system. The PDE is the product of three factors

$$PDE = \epsilon_{gm} \cdot Q_E \cdot P_{tr} \tag{1.1}$$

$\epsilon_{gm}$  is called filling factor or geometry factor; it is defined as the ratio of the effective detection area to the total detector area. Since quenching resistors and conducting metal will also need space on the detector area,  $\epsilon_{gm}$  is always smaller than one.  $Q_E$  is called quantum efficienty and is defined as the probability of carrier generation for incoming photons.  $P_{tr}$  is the triggering probability and refers to the probability that a created carrier will trigger an avalanche process. Different structures and doping patterns are studied to enhance the PDE. They will be analyzed later in Chapter 2 section 2.22.

#### 1.3 Outline of the Thesis

The thesis is divided into four parts. Chapter 2 will describe different SiPM structures and discuss several key points in SiPM detector design. In addition, the physics behind all important specifications will also be introduced. Chapter 4 and 5 will concentrate on electronics design details for two different SiPM readout schemes, charge readout and fast timing readout. Details about two ASIC chips, i.e. KLauS and STiC will be introduced in these two chapters. Chapter 6 is a summary of all the test results of these two ASIC chips. In Chapter ?? the thesis is summarized.

# Chapter 2

# Silicon Photomultipliers -Structures and Physics

Various physical aspects of silicon photomultipliers will be investigated in this chapter. The scope covers the evolution of these Geiger mode avalanche diodes, their structures and particular properties such as breakdown voltage, temperature coefficient, photon detection efficiency, crosstalk, afterpulse as well as thermal noise. A realitatic electrical model will also be introduced at the end of this chaper which will be used later as a basis for the SiPM readout electronics design. In addition, some interesting detector structures of Single Photon Avalanche Diodes (SPAD) will be described and compared to the SiPM design. SPADs and SiPMs have similar working principles and basic structures. However, SPADs are normally designed with conventional CMOS technology while SiPMs require special production steps.

# 2.1 SiPM Development Overview

The invention of Geiger Mode Solid State Photon Counter dates back to the 1960s. The related Geiger mode microplasma breakdown phenonema inside silicon was extensively investigated in different laboratories at that time. Explicit theories were established and summirized by McIntyre from the RCA company with a paper published in 1961 [4]. At the same time, Haitz at the Schockley Research Laboratory [5] had experimentally proven the concept in a uniform p-n junction with bias exceeded breakdown voltage by a few volts.

Nevertheless, it was only in the 1980s that prototypes of "modern" conventional Silicon Photomultipliers were invented in Russia [6][7]. There are two difficulties in fabricating and using this kind of device. The first difficulty is to fabricate a device with a controllable high multiplication gain. This is because of the large breakdown voltage variation due to heterogeneities inside silicon wafers. Although the p-n junctions are uniformly designed and the breakdown voltage is intended to be uniform over the whole junction area, the heterogeneous spots inside the junction will always cause about 0.1-0.2V breakdown voltage variation over the whole depletion area. Because the avalanche multiplication factor has a very sharp dependence on the applied voltage, the avalanche will only be localized around spots with lower breakdown voltages. Consequently, the gain of the devices is not well under control and varies from device to device. Fortunately, this problem can be solved by using a local negative feedback,

such as a large quenching resistor in series with the p-n junction. The sharp dependence of the multiplication factor will be smoothed and the breakdown voltage variation can be extensively suppressed. The device gain can thus stay under control. The second difficulty is related to the detector application. Since the p-n junction works as a binary counter as described in the prvious chapter, it cannot provide any information on the incoming photon number since the reponse for single and multiple photons are identical. The solution to this problem is to connect thousands of small Geiger mode avalanche pixels in parallel. Hence, each single pixel instead of the the whole detecor behaves as a binary counter. The response of the new device is now linear with the incoming photon number as long as the light is evenly spread over the whole surface and the flux duration is much shorter than the device dead time. All these motivations gave birth to the idea of building Geiger mode avalanche diode pixel array the using Metal-Resistor-Semiconductor (MRS) technology [8], which involves a special resistive layer between the conducting metal and the silicon wafer [9][10].

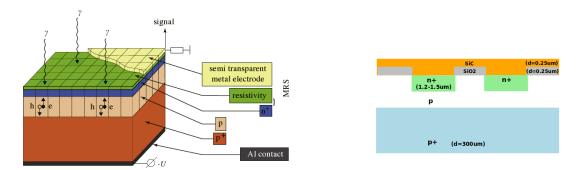

Fig. 2.1: Illustration of an MRS profile [11] Fig. 2.2: Improved MRS SiPM profile with SiO<sub>2</sub> layer

Figure 2.1 illustrates the MRS SiPM profile. It has a  $n^+$ -p- $p^+$  doping structure which is quite similar to what is displayed in Figure 1.3. However, the quenching in the MRS SiPM is realized by a whole resistive layer instead of discrete components as introduced in last chapter. On top of the resistive layer, there exists a semitransparent conducting metal layer for detector bias connection; originally, the semitransparent metal layer was composed of Ti or Ni with a thickness about  $0.1-0.2\mu m$  [12][13][14]. The metal layer is covered by an antireflection coating (ARC, Si<sub>3</sub>N<sub>4</sub>). And for the resistive layer a material with a wide energy gap and suitable conductivity is used. It consists of 5-6 $\mu m$  thick silicon nitride/carbide or amorphous hydragenerated silicon deposited using the ion-plasma evaporation process. Silicon Carbide (SiC<sub>4</sub>) is often used in red sensitive designs and Silicon Nitride (Si<sub>3</sub>N<sub>4</sub>) aims for SiPMs sensitive to green light. The multiplication zone is located at the n<sup>+</sup>-p interface which is about 1-2 $\mu m$  thick. It is fabricated by first growing an epitaxy layer on top of the 300-500 $\mu m$  p<sup>+</sup> substrate and then ion-implanting the n<sup>+</sup> [12] layer. The thin resistive layer has a very low conductivity in the horizontal direction; therefore the impact ionization and quench process can be confined inside each pixel junction area.

In principle, there are two major drawbacks of MRS SiPMs. The first darwback is their low production yield. This is because of the extreamly thin resistive layer (100-200nm) that often causes short circuits on silicon wafers. The second drawback is their low sensitivity in the UV or blue region. This wavelength region is required by many scintillation light detection systems. The reasons for a low blue/UV PDE(1-2% @ 480nm [12]) are three-fold: (1) The large inter-pixel distance (low filling factor). The large distance is used to suppress crosstalk effect because of the electrical coupling effect

on the resistive layer. (2) the non-optimized doping structure; for UV light ranging from 200-400nm significant light absorption happens within the first 2  $\mu m$  under the surface before the photons reach the junction area and the intended photo-electron generation and drift zone (p zone in the figure); the generated electrons are collected immediately by the metal electrods and the remaining holes are used to trigger the avalanche; however, as will be dicussed later in section 2.3.6, holes have a much smaller triggering efficiency ( $P_{tr}$  in equation 1.1) than electrons thus making the effective PDE pretty low; (3) the opaqueness of the resistive layer to the blue/UV photons.

In the 1990s, different solutions have been proposed which can at least partially solve the problems of MRS SiPMS. The main idea is to use  $SiO_2$  as a buffer layer between neighbouring pixels. Figure 2.2 illustrates one of several designs implementing this idea [15]. The resistive layer made of amorphous silicon/SiC [15] (later high value polysilicon [16]) is added on top of the  $SiO_2$  layer as illustrated in the figure. The silicon dioxide provides better decoupling than the resistive layer thus helps to enhance the filling factor from 1% to 25%. It also works better as an insulator than the previous resistive layer so that less short circuits occur and a high production yield is reached. This device was fabricated by MEPhI Moscow and other examples including designs from CPTA and Obninsk, Russia, can also be found [17][18][19].

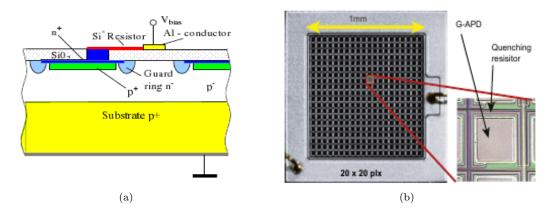

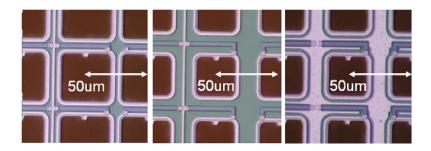

Figure 2.3: (a) Doping profile of MEPhI SiPMs (b)Picture of Hamamatsu MPPC

The next evolution step accomplished a new milestone since it completely solved the yield problem and soon led to mass production. Vendors such as CPTA/Photonique [19],MEPhI/PULSAR [16], FBK-IRST [20] and Hamamatsu [2] are still producing SiPMs based on this particular structure (and its variaties). Figure 2.3 depicts its typical profile and a microscopic surface picture. As implied by the pictures, the quenching resistor is now made of a discrete polysilicon resistor and is moved away for the pixel sensitive area. Since the resistor is now far away from the junction, it will no longer cause any short circuit problem. The silicon dioxide extends now over the whole surface; therefore the overall quantum efficiency has been increased due to its transparency to blue/UV light.

Several remedies have been proposed on the basis of this structure to solve the remaining PDE problems described before for the MRS SiPM: (1) Using an optical trench to solve the filling factor/crosstalk trade-off as proposed first by CPTA/Photonique [17] and followed up by others; the optical trenches (SiO<sub>2</sub>) were fabricated and filled up with opique materials as illustrated in Figure 2.4. Optical crosstalk between neighbouring pixels can been extensively diminished by this method and the inter-pixel distance can also be reduced. The overall device crosstalk can be decreased from 10-20% to 1-3% [18][3] using optical trenches. It also raises the filling factor up to 60-70% [21] on account of the closer pixel allocation; (2) Tuning the doping and junction/epitaxy thickness so as to guarantee that the avalanche

Figure 2.4: Doping profile of a MPPC from Hamamatsu, grooves are designed to reduce optical crosstalk

is always triggered mainly by electrons; this can be done either by opening the illumination window on the back side [4][12] or by keeping the window on the top side but using inversed doping polarities e.g. a p on n substrate [22]. Detailed explanations will be provided in section 2.3.6.

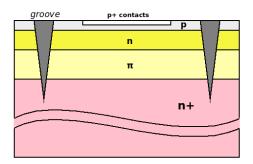

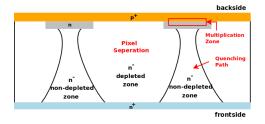

Fabrication of the high value quenching resistor O(100k - 1M) is always the cost driver for production. Special process steps are necessary in manufacturing, thus making them not compatible with modern CMOS technologies. Therefore, structures without resistors have been investigated. Very good examples within various efforts come from JINR(Dubna) [14] and Semiconductor Labor Munich (HLL München) [23]. The former utilizes a special thin p<sup>+</sup> charge channel underneath SiO<sub>2</sub> connecting the p-n junction to a corresponding drain terminal as demonstrated in Figure 2.5. The charge generated during multiplication will be transferred through this p<sup>+</sup> charge channel to the drain area such that this special layer functions as a conventional quench resistor. The corresponding resistance is adjusted by tuning shapes and doping concentrations of the p<sup>+</sup> charge channel. Several pixels share one drain terminal, which makes the device possibly work like a CCD if the array can be read out and reset/cleared in a certain sequence. HLL München has developed a back illuminated silicon photomultiplier integrating a non-depleted doping volumn as a quenching path as shown in Figure 2.6. The n<sup>-</sup> doping is properly designed such that the p<sup>+</sup>-n<sup>-</sup>-n<sup>+</sup> in the middle forms a large junction that works as a separation for neighbouring pixels. The non-structured p<sup>+</sup> back side is totally open for luminance without any space occupation from quenching resistors. Therefore, a higher filling factor is promised compared to the conventional SiPM structure. A filling factor of 90% and a PDE of more than 60% for blue light have

Fig. 2.5: surface charge passive quench scheme

Fig. 2.6: backside illuminated SiPM

already been measured. The quenching path demands a relative high ohmic bulk with a thickness of about 30-70 $\mu$ m which can be produced by either epitaxy growth or wafer bonding technology. The only problem of this design is that the quenching resistor functions as a JFET (p<sup>+</sup> as gate, n anodes as drain,  $n^+$  as source) such that the instantaneous resistance of the path increases as the current decreases; due to this the recovery time will be longer than the SiPMs using the conventional polysilicon quenching resistors. This back illuminated structure also promises the possibility to attach the readout electronics to the frontside by bump-bonding. This topology is able to preserve the high integration density without losing any photon detection efficiency. Variants of this structure can be found in [24][25].

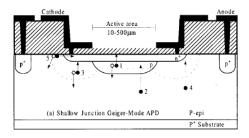

As a complement to the aforementioned effort, there are institutions and manufacturers who are investigating structures and technologies compatible with conventional planar/CMOS processes. Instead of implanting the junction on an epitaxy layer with well-defined depth, a relative shallow junction is implemented on silicon wafers. SenSL (Cork, Ireland), ST Microelectronics (Catania, Italy) and Radiation Monitor Devices (RMD, USA) are among such vendors. SenSL fabricates the diode array on an epitaxy grown p-type bulk silicon using CMOS  $1.5\mu m$  technology. Each pixel has a n<sup>+</sup>-p-p<sup>+</sup> structure similiar to the MRS SiPMs (p is the grown epitaxy layer). The n<sup>+</sup> area is diffused onto the substrate and thus forms a shallow p-n junction [26]. Although the device is fabricated on an epitaxy grown wafer like others, the thickness of the epitaxy layer is fixed and not tailored for detector performance.

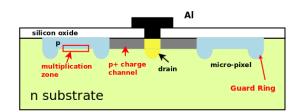

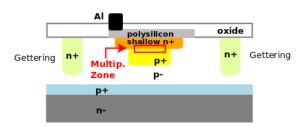

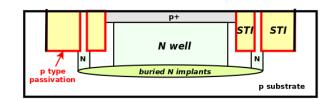

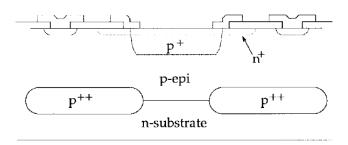

Fig. 2.7: SiPM pixel profile from STM.

Fig. 2.8: SPAD with shallow junction

Figure 2.7 displays the cross section of the silicon photonmultiplier pixel from ST Microelectronics [27]. The device is fabricated on a silicon planar technology [28]. The fabrication starts with a n<100> substrate with a p<sup>+</sup> buried layer implanted on it. Another boron doped epitaxy is grown on the p<sup>+</sup> layer. The buried p<sup>+</sup> layer helps to improve the detector timing response since it suppresses the diffusing effect of the photo-generated carriers inside the undepleted region (will be explained in Chapter 5 section 5.1.1). A local gattering process with heavily doped POCl<sub>3</sub> diffusion is implemented in order to enhence the purity. Then comes the p<sup>+</sup> enrichment diffusion, annealling, shallow n<sup>+</sup> diffusion and polysilicon deposition. The dark rate is about 10Hz for  $100\mu m^2$  and has a quite linear relationship with the detector area. The PDE peaks at around 600nm with 40% efficiency; an enhancement for the blue and UV region can be achieved by reversing the doping type of p on n epitaxy [29].

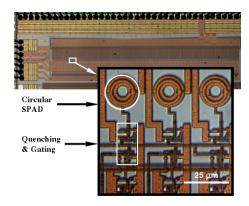

Apart from the cheap cost of production, the reason to design the detector array with a conventional CMOS technology is its compatibility with standard CMOS circuit cells. Using CMOS technologies the readout circuit can be placed right beside the pixel diode and the information captured by the pixel can be preserved with minimal distortion. Although silicon planar technology (CMOS) is not able to produce deep trenches between neighbouring pixels, crosstalk effect can be suppressed by the presence of the anxiliary circuits, which have almost the same size as the detector pixel such that large inter-pixel distances are guaranteed. EPFL [30], TU Delft [31], Uni Milano [32], UCSD [33] and

Philips [34] etc. have been engaged in developing this CMOS integrated pixel/readout detector; and such detectors have been given a new name - Single Photon Avalanche Diodes (SPADs). SPADs have almost the same working principle as SiPMs except that active circuits are used for quenching instead of a passive resistor. In this section, the SPAD pixel structure will be emphasized; the corresponding active quenching circuits will be discussed in section 2.2.3.2.

Fig. 2.9: Double epitaxy SPAD profile

Fig. 2.10: SPAD with shallow trench isolation

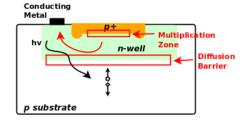

Figure 2.8 shows a typical cross section of an original SPAD pixel [35][36]. The junction usually has a shallow or medium depth and is generated by implanting or diffusing a layer of p<sup>+</sup> doping onto a n-well. The high field multiplication zone sits directly underneath the p<sup>+</sup> doping. Unlike the tailored n<sup>+</sup>-p-p<sup>-</sup>-p SiPM structure, SPADs do not have a intended drift zone for photon-generated carriers (p<sup>-</sup> used for drift in SiPM). Photons often generate electron-hole pairs in the undepleted zone underneath the avalanche junction as shown in the figure. These carriers will diffuse into the multiplication zone and trigger Geiger mode avalanche. But since the diffusion constant is really slow, the timing performance will be seriously deteriorated by these carriers. Therefore, the shallow junction between n well and the substrate is designed to suppress the diffusion, which otherwise causes a long and slow tail in the pixel timing spectrum.

As the development continues, the original pixel structure has been evolved into different improved versions. Figure 2.9 shows an improved version with double epitaxy layers [37]. Another highly doped layer is inserted between the substrate and lightly doped epitaxy to further improve the timing performance. The idea is to further reduce the undepleted region in the n-well (between the multiplication zone and diffusion barrier in Figure 2.8). But if the depth of n-well is too small, the effective resistance experienced by the avalanche generated carriers (path indicated by the arrow in the Figure 2.8) will be quite large thus reducing the output current. Therefore, a low resistive highly doped layer can be implanted such that a high output current can still be expected. In principle, Figure 2.9 and Figure 2.7 have the same pixel doping profile except that polysilicon is used in Figure 2.7 and active quenching circuits are used in Figure 2.9.

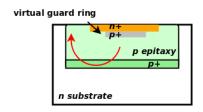

Figure 2.10 shows another structure using the so called Shallow Trench Isolation (STI) technique [38]. In principle, it is the same principle as the one shown in Figure 2.4, except that the trenches are relatively shallow. This technique is oringinally used in CMOS technology for prevention of punch-through and latch up and is compatible with the whole fabrication process [39]. As will be explained in section 2.2.2, pre-mature breakdown is eliminated by truncating the curved field at the edge of the p-n junction by the shallow trench [40]. In addition, the distance between neighbouring pixels can be extensively reduced, promising a higher filling factors. Nevertheless, STI has a huge impact on the dark count rate because sidewall damage occurs during trench etching such that a large amount of deep level carrier generation centers are created. The problem becomes even more significant because STI

is located directly next to the avalanche junction. The remedy, as illustrated also in Figure 2.10, is to use passivation p<sup>+</sup> implants around the STI like a glove. The p<sup>+</sup> concentration decreases gradually up to the n-well so as to minimize the electric field for edge breakdown. The dark count rate is highly suppressed since a very short mean free path is provided for the minority carriers generated at the p<sup>+</sup> glove surface; this drastically reduces the probability for these carriers to enter the active area [31]. Figure 2.11 shows a typical surface microscopic photo of a SPAD array; the auxiliary quenching and discrimination circuits can be clearly seen on the picture.

Figure 2.11: Microscopic photo of a SPAD array system surface [41]

Normally, SPAD devices have a very good timing resolution because the signal processing is implemented pixel-wise, and the circuit performance degradation from large detector capacitance is avoided. A single pixel timing resolution better than 30ps has already been reported [33]. However, SPADs still have the problem of low filling factors, although this can be solved by using diffractive films or micro-lenses [42]. Up to now, very low filling factor and large detector area size (due to the anxiliary circuits) is the common problems to all SPAD devices.

# 2.2 Key Points in Silicon Photomultiplier Design

Design and fabrication of SiPM or SPAD device certainly involve very delicate procedures. For simplicity, only a few points will be addressed here as they are quite useful in both understanding the device performance and readout electronics design.

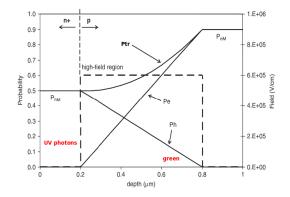

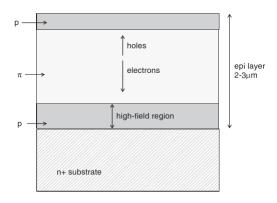

#### 2.2.1 Avalanche Junction with Reach Through Structure (RTS)

Reach through structures are well studied structure that have been implemented oringinally in silicon APDs because of their advantage in terms of enhancing the photon detection efficiency [43][44]. Because of this, SiPM pixels are often designed using this structure (as can be inferred from the doping profile plots in last section). SiPMs from MEPhI [16], CPTA [45], FBK-IRST [46] and Hamamatsu [47] are good examples. The pixel cell is normally implanted with a doping profile of  $n^+$ -p- $\pi$ - $p^+$  or  $p^+$ -n- $\pi$ - $n^+$  as illustrated in Figure 2.4.  $\pi$  reprents a very light p/n doping (almost intrinsic) with a relative thick width compared to other heavily doped areas. Once the detector bias voltage is applied, the depletion zone will start from the  $n^+$  region, crosses the thin p layer and "reaches through" the  $\pi$  region finally ending in the narrow  $p^+$  area. According to studies of APD structures [43], it is still

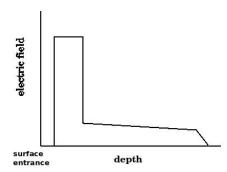

Figure 2.12: Doping sketch and electric field inside RTS

appropriate to model the middle part as instrisic silicon as shown in Figure 2.12, even though the p region somehow overlaps with  $n^+$ . This approximation simplifies the calculation keeping the calculated electric field almost the same. The electric field can be analytically obtained by solving the Poisson equation:

$$-\frac{d^2\phi_i}{dx^2} = \frac{\rho(x)}{\varepsilon_s} = \frac{1}{\varepsilon_s} [N_D^+(x) + N_A^+(x)]$$

(2.1)

Here,  $\rho(x)$  denotes the charge density as e.g. shown in Fig 2.12. The electric field can be calculated by

$$E = -\frac{d\phi_i}{dx} = \frac{1}{\varepsilon_s} \cdot \int \rho(x) \ dx \tag{2.2}$$

If the  $n^+$  and p doped regions are treated as delta functions and for the intrisic region one assumes  $\rho = 0$ , the electric field is the one displayed in Figure 2.12. As expected, the high field locates between the  $n^+$  and p regions. In addition, since the  $\pi$  layer has a very light doping concentration, the electric field tends to be almost flat in the  $\pi$  region, which is quite ideal for a carrier drift. As soon as electrons and holes are created by a photon within this area, electrons will be separated immediately from holes and then tigger an avalanche inside the junction.

During the optimization stage of a SiPM design, the thickness and doping concentration of the three p-type layers can be modified so as to meet different performance requirements. The most important is the trade-off of the width of the avalanche zone. A higher PDE and single pixel timing resolution requires a thicker width of the multiplication zone since it can collect more electrons right after their creation. But a wider multiplication zone also leads to a higher dark court rate, which in turn affects the overall performance [45]. Other optimization methods, such as tuning the depth of the avalanche and drift zones also have impacts on photon detection efficiency, because the actual photon-generation position has a strong dependence on the photon wavelength, i.e. photon penetration length. Thus, different PDE requirements may lead to different doping depth [22].

#### 2.2.2 Pre-mature Breakdown (PEB) Prevention

Pre-mature breakdown refers to a breakdown happening at junction edges before the intended depletion zone reaches its breakdown state. This is due to the fact that the curvature at corners always causes a higher electric field compared to the designed depletion zone. Therefore, the multiplication will confine at the edges and cannot spread to the whole device. It is one of the most serious problems

in SiPM/SPAD design since it prevents occurrence of Geiger mode avalanche in the desired structure. There are four popular ways of solving this problem, they are namely implementations of diffused guard rings, virtual guard rings, floating guard rings or shallow trench isolation (STI) structures.

The diffused guard ring structure is the PEB solution originally used in 1964 by Haitz [5]. It utilizes light doping to enclose the topmost concentration layer so as to reduce the electric field as illustrated in Figure 2.3, 2.5 and 2.8. Examples are SiPMs from MEPhI [16], CNRS [48] and Dubna-Zekotec [14]. However, the PDE will be degraded by this structure because the photon-generated carriers will have the possibility to drift into the guard ring thus reducing the efficient photo-electron creation probability. Timing performance will also be affected due to this reason. In addition, the large guard ring size leads to a low filling factor.

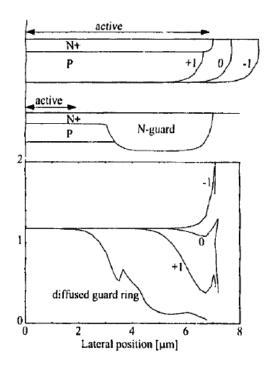

Figure 2.13: Scaled electric field calculated for diffusion and virtual guard rings [49], explanation see text

An improvement is to have a so-called virtual guard ring structure as illustrated in Figure 2.9 with n<sup>+</sup> extending several microns over the p<sup>+</sup> doping border. Figure 2.13 shows a simulated electric field (scaled) of virtual guard rings with different extension size as well as its comparision to the diffused guard ring. The position "-1" shows an edge electric field twice as large as the center of the depletion zone thus indicating no premature prevention. Position "1" and "0" has perfect PEBs except that the latter has a larger effective area. In addition, the virtual guard ring also has a much broader multiplication zone compared to a diffusion ring of the same size. This structure was originally invented for commercial CMOS SPAD [37] in order to embed another epitaxy layer under the p-well in Figure 2.9 as a virtual guard ring is vertically much thinner than a diffused guard ring. This PEB approach has been implemented in many CMOS or CMOS compatible planar technology SPADs such as the ones from SenSL [26] and ST Microelectronics [28] (Figure 2.7). Meanwhile, back-illuminated SiPM designed by HLL München (Figure 2.6) also uses this method.

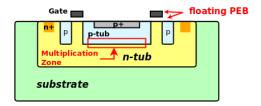

Figure 2.14: Floating guard ring structure to prevent premature edge breakdown

The EPFL SPAD group has proposed a structure with floating gate PEB control [50], which is shown in Figure 2.14. The multiplication zone is located beneath the p-tub. A negative voltage can be applied to the two gates beside the p-tub so as to reduce the electric field strength at the p-tub borders and also somehow extend the effective area toward the two small p-tubs outside. Although this technology is compatible with the whole CMOS production process, it still violates several design rules. In addition, the area occupied by the extra peripheral control will lead to a reduction of the filling factor.

The most popular PEB prevention structure is to use trenches to separate pixels. It can be deep trenches used by CPTA [21] and Hamamatsu [47] or shallow trenches used in SPAD devices [31][38]. The trench truncates the junction edge such that the edge effect is removed automatically. This method not only leads to a very high filling factor but also reduces the cross talk probability substantially.

#### 2.2.3 Quench Circuits

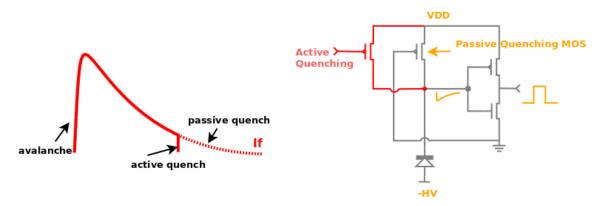

As already mentioned before, there are two ways of providing negative feedback to each avalanche pixel, namely passive and active quenching circuits. Passive quenching simply connects the pixel through a large resistor to the high voltage bias. Once photon generated carriers initiate impact ionization inside the pixel, the voltage drop across the resistor due to the large avalache current will reduce the bias voltage back to breakdown voltage, such that the pixel can return to the quicscent state. Active quenching uses active circuits to control the pixel bias voltage, and its response is quite fast compared to the passive method; it has quite a few advantages with respect to the passive methods but the control unit takes up more space on the detector surface thus decreasing the filling factor. Furthermore, the control circuits are usually built by gate circuits so that it can only be implemented in detectors made of standard CMOS technologies.

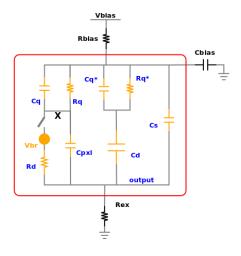

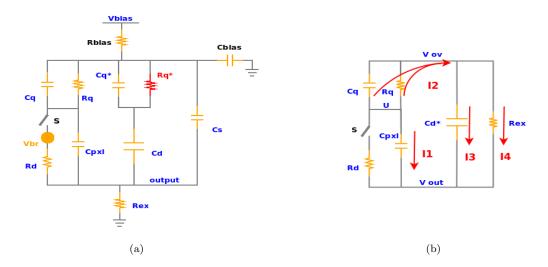

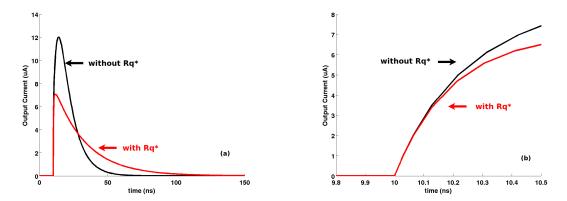

#### 2.2.3.1 Passive Quench Circuit (PQC)

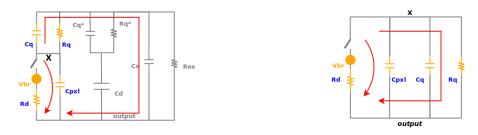

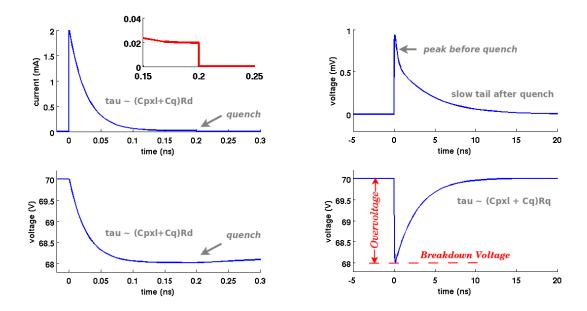

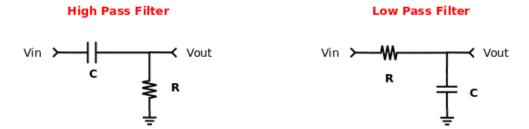

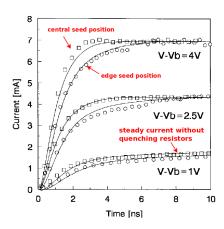

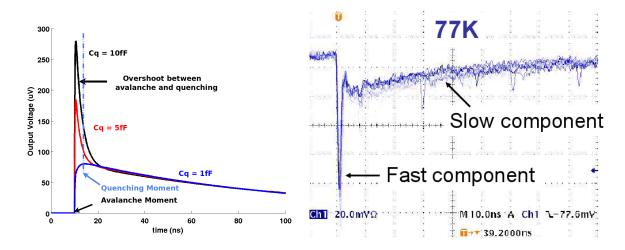

The most important point concerning passive quenching is to determine the minimum value of the passive resistor or the maximum overvoltage that can be applied. In principle, the method takes advantage of the statistical nature of the avalanche process. The multiplication process can be switched off as long as the amount of carriers generated per unit time is small enough such that the avalanche cannot continue due to the lattice collisions etc. The current inside the avalanche pixel has a shape illustrated in Figure 2.15. It increases to a very large current at the moment of the avalache and then slowly decreases to a final state current  $I_f$  (Detailed explaination in section 2.4). The correct choice of the quenching resistor value is done by setting a proper final current value which guarantees that the

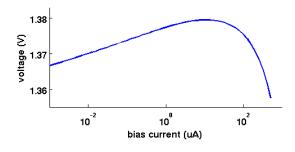

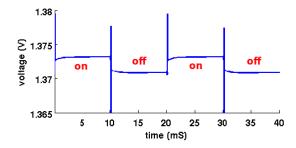

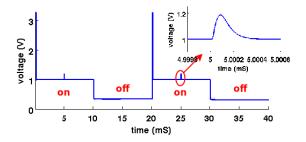

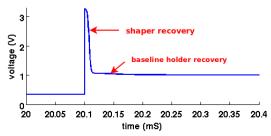

amount of carriers generated per unit time is too small to sustain the impact ionization process. The final current value is determined roughly by  $I_f = V_{ov}/R_q$ . Here,  $V_{ov}$  denotes the overvoltage and  $R_q$  is the quench resistor. Studies [5] show that the impact ionization process will be turned off once  $I_f$  is below a certain threshold value. Actually, there exists no sharp definition of this threshold value, but only a probability distribution for quenching as a function of the current. Haitz concluded that for  $I_f$  less than  $100\mu A$  the microplasma phenomenon tends to stop at some point, but the exact quenching time is uncertain with a large jitter if  $I_f$  is really close to  $100\mu A$ . A higher  $I_f$  also leads to higher power consumption since it also takes more time for the avalanche to switch off. Thus, as a rule of thumb, Cova et al. [51] have proposed  $20\mu A$  as a practicle and safe threshold value. This value amounts to  $50k\Omega/V$ , which means the maximum safety overvoltage to be applied should be about  $R_q/50k(V)$ . This criterion is quite valuable, since it indicates the maximum decrector operation voltage, e.g. for a Hamamatsu MPPC with  $R_q \approx 200k\Omega$ , the maximum  $V_{ov}$  is about 4V. If the overvoltage is too high or  $R_q$  is too small, the device will either be thermally damaged or remain at a steady current state just like a forward biased diode. More details about PQC and its impact on waveforms will be discussed in section 2.4.

Figure 2.15: Waveform of an Active/Passive quench Figure 2.16: Passive quench with a transistor [52]

MOSFETs biased in the triode region can also be used as quench resistors [53]; this is used in some SPAD devices as shown in Figure 2.16. The PMOS gate is connected to GND to maximize the gate source voltage and to gurantee the triode mode operation. Generally speaking, the idea is to utilize the gate voltage to control the channel width beneath the oxide layer so as to modulate the channel resistance of the MOSFET. It is quite similar to the one used in the so-called back illuminated SiPMs designed by the HLL München (Figure 2.6) except that a JFET is formed there below the avalanche diode. Certainly, avoidance of polysilicon for quenching resistors not only improves the filling factor but also simplifies the fabrication. However, the effective resistance of the charge channel also depends on the current amount flowing through; and it is quite normal in this case to observe relative long tails in the pixel recovery stage, i.e. longer dead time.

#### 2.2.3.2 Active Quench Circuit (AQC)

The idea of the active quenching is to have active circuits to reset the voltage bias condition as soon as the signal is readout and information is stored. The simplest one is to have a transistor in parallel to the quenching MOSFET as marked red in Figure 2.16 [54]. The gate terminal of the active

quenching transistor is controlled by a pulse which is a delayed copy of the output digital signal so that the detector cathod can be reset to initial VDD value much faster than it is reached in case of the passive quenching illustrated in Figure 2.15. Since the reset circuit requires special transistor libraries, this method is often used in deep sub-micron CMOS technology based SPAD array designs because of the availability of well-designed digital CMOS libraries. Different active quench circuits have been explored extensively; examples can be found in [51][55].

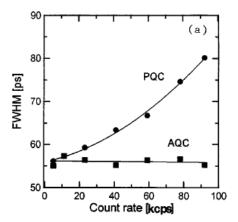

Figure 2.17: Comparision of SPAD timing performance for PQC and AQC [51]

Active quenching is more prominent than passive quenching in terms of pixel signal timing because the diode pixel has a much smaller dead time and all pile up effects from dark pulses or high rate incoming signals can be suppressed. Cova et al. [51] reported the comparision of the SPAD timing performance for the two methods; the results are given in Figure 2.17 which shows the FWHM of timing spectra recorded for different light pulse frequencies. Almost no pile up effects can be observed for the AQC circuit, while for the PQC circuit the resolution clearly degrades for large count rates. A long reset pulse also has a positive impact for after-pulse and thermal noise effects since the after-pulse probability is proportional to the square of the overvoltage. Reducing the overvoltage by the reset pulse leads to a low probability for field assisted tunnelling in dark count generation as will be described in more details in section 2.3.3 and 2.3.4.

# 2.3 Performance of Silicon Photomultipliers

The most important figures of merit of Silicon Photomultipliers are their photon detection efficiency (PDE), dark count rate (DCR), single photon timing resolution (SPTR), after-pulse and cross-talk probability as well as their temperature coefficient. In this section, the physics background of these aspects will be reviewed with the exception of the single photon timing resolution, which will be revisited in Chapter 5.

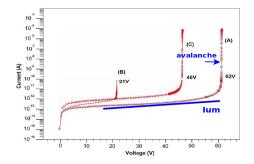

#### 2.3.1 Breakdown Voltage and Temperature Dependence

The breakdown voltage of a p-n junction is related to the doping concentration and profile as well as temperature. It can be determined by the ionization coefficient of electrons and holes in the avalache

process.

The deriviation of the breakdown voltage can be started from the simple breakdown condition [56]

$$\int_0^{W(v)} \alpha(v)dx = 1 \tag{2.3}$$

Here,  $\alpha$  is the effective ionization coefficient (defined as number of electron-hole pairs generated per unit length), which combines both electron and hole effects [57] and W is the junction width. Both W and  $\alpha$  are dependent on the overall bias voltage v. Therefore, Equation 2.3 sets a criterion on the minimum voltage, i.e. the breakdown voltage, that can sustain the impact ionization process. In the case of a one-sided abrupt p-n junction with light doping on one side while the other side can be approximated as a delta function, if the temperature effect is neglected, the breakdown voltage is [56]

$$V_{br} = \frac{\epsilon_s E_m^2}{2qN} \tag{2.4}$$

Here  $\epsilon_s$  is the silicon dielectric constant,  $E_m$  is the maximum field inside the junction and N is the doping concentration for the lightly doped side. Actually, although the pixel diode might not fulfill the assumption of a one-sided junction, qualitatively speaking, the breakdown voltage is still roughly inverse proportional to the doping concentration.

Solving the temperature depedence of the breakdown voltage is a rather complicated process. Qualitatively, it can be explained by optical phonons inside the lattice. Phonons are quanta of lattice vibrations. The higher the temperature, the more the vibration. The mean free path of carriers will thus decrease with temperature, thus accumulating less kinetic energy inbetweeen two collisions. Hence, a higher electric field, i.e. a higher voltage is required to initiate breakdown under higher ambient temperature.

Of the two parameters in equation 2.3, only the ionization coefficient  $\alpha(v)$  is temperature dependent;  $\alpha(v)$  is expected to be related to:

$$\alpha \sim C(T) \cdot exp[-p(T)/E]$$

(2.5)

where C(T) and p(T) are coefficients determined by fits to experimental data depending on the ambient temperature T. According to equation 2.3 and 2.5, solving  $dV_{br}/dT$  can be reformulated as solving dC/dT and dp/dT since the electric field does not change with respect to temperature. Baraff [58] has proven that the ionization coefficient is related to three parameters: the carrier free mean path  $\lambda$ , the ionization threshold energy  $E_i$  and the average energy loss in a collision  $E_r$ . Sze [59] et al. have provided an empirical formula describing the relation of  $\alpha$  to these three parameters; this was proven experimentally later with data from different doping profiles [60]. The product of  $\alpha$  and  $\lambda$  follows an exponential function of  $E_r$ ,  $E_i$  and  $\lambda$ , which can be expressed as

$$\alpha \cdot \lambda = f(E_i, E_r, \lambda) \tag{2.6}$$

Since the temperature dependence of  $E_r$ ,  $E_i$  and  $\lambda$  can be easily determined by experiments, dC/dT and dp/dT can be calculated using Equation 2.5 and 2.6. Once dC/dT and dp/dT are known, the

relative temperature coefficient of  $V_{br}$  can be calculated again using Equation 2.3. The result is [61]

$$\frac{1}{V_{br}}\frac{dV_{br}}{dT} = \frac{2}{1 + g + p \cdot \sqrt{\frac{\epsilon_s}{2Nq}}} \cdot \left[ (g + p \cdot \sqrt{\frac{\epsilon_s}{2Nq}}) \cdot \gamma - \psi \right]$$

(2.7)

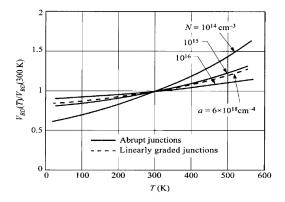

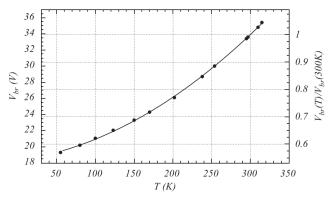

where g is a constant related to doping structure, which equals to 0.63 for an abrupt p-n junction.  $\gamma = dC/dT$  and  $\psi = dp/dT$  are the relative temperature coefficients for C and p in equation 2.5; they can be considered to be constant. Equation 2.7 results in a quasi exponential relation between the breakdown voltage and the temperature, as the right hand side can nearly be treated as constant except for p(T). Figure 2.18 shows several theoretical cruves of the breakdown voltage dependence on

Figure 2.18:  $V_{br}$  vs. T for different dopingi profile [56]

Figure 2.19:  $V_{br}$  vs. T for an IRST SiPM[62]

temperature which look quite similar to the curve measured with FBK-IRST SiPMs from cryogenic to room temperature in Figure 2.19. Equation 2.7 and the plots above are of great importance since they have revealed the fact that there is no linear relation between  $V_{br}$  and T; however, in a small temperature range (200-300K) and for a smooth curvature, e.g. for Hamamatsu MPPCs [63], a linear approximation of this exponential dependence is possible. SiPMs from FBK-IRST have been measured to have a slope of about 80 mV/K; for MPPCs from Hamamatsu the value is about 50 mV/K.

#### 2.3.2 Dynamic Range and Saturation Effects

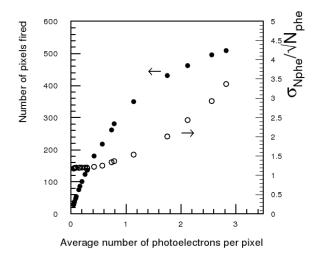

The response of silicon photomultipliers to an incoming photon flux obeys an exponential relation rather than a linear dependency due to the limited pixel number. The analysis can be separated into two steps: first calculate the total number of pixel-firing photons using a PDE related binominal probability function and then allocate the fired photons into all available pixels. The problem itself can be simplified by counting how many pixels contain at least one fired photon. Similar to the occupancy problem of Urn Models [64], the average number of fired pixels and its variance [65] for n photons on m pixels can be expressed as a function of the photon detection efficiency  $\xi$

$$\bar{N} = m[1 - (1 - \frac{1}{m})^{n \cdot \xi}] \tag{2.8}$$

$$\sigma_{\bar{N}^2} = m(m-1)(1-\frac{2}{m})^{n\cdot\xi} + m(1-\frac{1}{m})^{n\cdot\xi} - m^2(1-\frac{1}{m})^{2(n\cdot\xi)}$$

(2.9)

If m approaches infinity, using the relation  $\lim_{x\to\infty}(1+\frac{1}{x})^x=e$ , the above equations transform into

$$\bar{N} = m[1 - exp(-\frac{n \cdot \xi}{m})] \tag{2.10}$$

$$\sigma_{\bar{N}^2} = m \cdot exp(-\frac{n \cdot \xi}{m}) \cdot [1 - exp(-\frac{n \cdot \xi}{m})] \tag{2.11}$$

Since the pixel number is usually very large, normally more than 100, it is always a good approximation to use the above response relation. It is thus clear that the average number of fired pixels is not linear with the number of incoming photons but follows an exponential relation, for a high intensity photon flux, i.e. SiPMs will suffer from saturation effects. Figure 2.20 shows a SiPM response curve with its

Figure 2.20: SiPM dynamic range and variance [16]

photon resolving variance. According to equation 2.10, assuming  $\xi \sim 20\%$ , SiPMs can keep a linear response up to 0.5 photon per pixel with an error of 5%.

Actually, the average and variance in equation 2.10 and 2.11 suggest that under the large pixel number approximation the number of fired pixels simply obeys Binomial Statistics, with a hitting probability  $p_0 = 1 - exp(-n \cdot \xi/m)$ . The probability function is

$$P(N) = \binom{m}{N} \cdot \left[1 - exp\left(-\frac{n \cdot \xi}{m}\right)\right]^N \cdot \left[exp\left(\frac{n \cdot \xi}{m}\right)\right]^{m-N}$$

(2.12)

Following the binomial nature of photon detection, different methods can be invented to extend the dynamic range without increasing the total pixel number [66]. If special microlens are designed such that a few pixels in the SiPM array have more probability to be fired than others, according to the binomial firing probability  $\sum_{i=1}^{n} p_{0,i}$ , the dynamic range will be extended and the variance  $\sum_{i=1}^{n} p_{0,i}(1-p_{0,i})$  will be decreased.

Since the pixel number is large and  $n \ll m$ , the probability function 2.12 can be further approximated by a Poisson Distribution, with the Poisson parameter  $\lambda_p = n \cdot \xi/m$ :

$$P(N) = exp(-\frac{n \cdot \xi}{m})(\frac{n \cdot \xi}{m})^N / (N!)$$

(2.13)

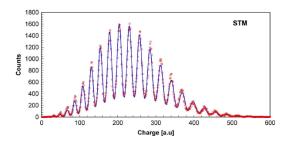

Figure 2.21: Single photon spectrums for SiPM with low crosstalk (left) and high crosstalk(right) [67]

This distribution function is often used to analyze SiPM single photon spectra (SPS) for which only several pixels have been fired. The spectra are a convolution of a Poisson distribution with several Gaussian peaks. Using a Poisson distribution is a quite accurate ansatz for SiPMs with low crosstalk and after-pulse effects; however, a higher crosstalk probability will make the spectrum more complicated as illustrated in Figure 2.21 [67]. In addition, for such measurements the incoming light pulse width should be relatively short compared to the recovery time of the detector so that all pixels are fired only once per light flash.

For a light pulse duration of the order of the recovery time, like e.g. light pulses from scintillation fibers with an exponential decay constant, the response is totally different. In such cases, the effective dynamic range can be extended according to the longer pulse width, since the pixels are already recovered when the later photons arrive. More complicated formulars including after-pulse and crosstalk effects as well as slow light pulse response can be found in [68].

#### 2.3.3 Dark Noise

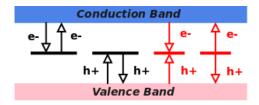

Dark noise is the limiting factor for low level photon detection because all noise generated carriers will also trigger Geiger mode avalanche pulses which are indistinguishable from photon-generated signals. If the noise rate is too high and the average time interval between two successive dark pulses are comparable to the pixel recovery time, pile-up effects will start to affect the pedestal of the DC coupled readout chain. The fluctuations of the pedestal can also be regarded as noise signal which sets the lowest signal processing limit. There are two mechanisms responsible for dark noise: band-to-band trap assisted thermal transistion and field assisted tunneling. Only one of them, i.e. the band-to-band transistion, is tightly related to ambient temperature.

Relatively speaking, it is quite improbable to induce carrier generation directly from the valence band into the conduction band in silicon even at high temperatures. The more probable way is a trap-assisted generation. In the thermal equilibrium, electrons and holes are continuously captured and released by trap centers as illustrated by the first two events in Figure 2.22. Since the capture and release are stochasitic processes, there exists the possibility that electrons or holes will transit from band to band. If the electron is first captured and soon after another hole is captured in this trap, the electron undergoes a transistion from the conduction to the valence band. Or a hole is first released from the trap and the remaining electron emitted into the conduction band, thus making the hole undergo a transistion from the valence to the conduction band. These two processes are illustrated as the last two events in Figure 2.22. The happening rate of these transitions is described by Shockley-Read-Hall

Figure 2.22: Capture and emission of electrons and holes by trap centers

(SRH) theory [56] with the formular

$$G_s = \frac{n_i^2 - n \cdot p}{\tau_{e0} \cdot (p + n_i \cdot exp[-(E_t - E_0)/kT]) + \tau_{h0} \cdot (n + n_i \cdot exp[(E_t - E_0)/kT])}$$

(2.14)

the  $E_t$  is the trap energy level and  $E_0$  is the Fermi level for intrinsic silicon;  $\tau_{e0}$  and  $\tau_{h0}$  are characteristic time constants of capture and release processes for electrons and holes; they are given by [56]

$$\tau_{e0,h0} = \frac{1}{\sigma_{e0,h0} \cdot N_t} \cdot \sqrt{\frac{m^*}{3kT}}$$

(2.15)

$N_t$  is the trapping center concentration,  $m^*$  is the effective mass of the charge carriers and  $\sigma_{e0,h0}$  is the capture cross section. In the depletion region  $p, n \ll n_i$  and if further defining  $\tau_g = \tau_{e0} \cdot exp[-(E_t - E_0)/kT] + \tau_{h0} \cdot exp[(E_t - E_0)/kT]$  one gets

$$G_s = \frac{n_i}{\tau_g} \tag{2.16}$$

Normally, the characteristic time  $\tau_{e0,h0}$  can be reduced by the factor  $1/(1+\Gamma)$  due to the existance of a high electric field with  $\Gamma \propto E \cdot exp(-E^2)$  [69]. Equation 2.16 implies a linear relation of  $G_s$  with the trapping center concentration  $N_t$  due to equation 2.15 which in view of the above considerations seems quite reasonable. The dark noise rate due to Shockley-Read-Hall effect is then simply given by

$$N_s = G_s \cdot P_{tr} \tag{2.17}$$

where  $P_{tr}$  denotes the avalanche triggering probability in Equation 1.1. For the silicon intrinsic carrier concentration, one gets  $n_i \propto T^{3/2} \cdot exp(-E_g/2kT)$  where  $E_g$  is the bandgap between valance and

Figure 2.23: Field assisted tunnelling for a high electric field

conduction band. In addition, according to equation 2.15  $\tau_g \propto T^{-1/2}$ . Therefore, the noise rate is

$$N_s \propto T^2 \cdot exp(-E_q/2kT) \tag{2.18}$$

The T<sup>2</sup> term implies a very strong dependence on the temperature. That's the reason why the SRH noise is the dominant dark noise source at room temperature.

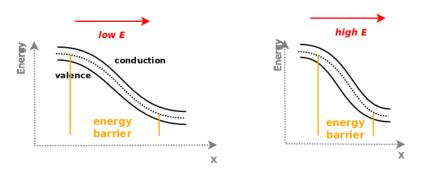

Field assisted tunnelling is another important dark noise source besides the trap-assisted transistion. It refers to band to band carrier transistions in the presence of a high electric field. The barrier width between valence and conduction band is  $E_g/2q\mathcal{E}$ . If the electric field  $\mathcal{E}$  is increased, the barrier width gets narrower and the carriers finally have the chance to tunnel to the conduction band. The carrier tunneling probability through a triangel barrier; as illustrated in Figure 2.23, can be calculated using quantum mechanics [70] yielding a tunneling noise rate of

$$G_t = D \cdot V_r \cdot \exp(-\frac{\pi^2 \sqrt{m^*} E_g^{3/2}}{\sqrt{2} q h E_m})$$

(2.19)

here, D is a constant,  $V_r$  is the junction reverse bias voltage and  $E_m$  is the maximum field inside the junction. The dark nosic rate is again

$$N_t = G_t \cdot P_{tr} \tag{2.20}$$

The field assisted tunneling dark noise has little dependence on the ambient temperature; the minor dependence is due to the temperature dependence of the bandgap  $E_g$ . The tunneling effect sets the lowest dark noise limit for cryogenic systems in which thermally initiated noise is eliminated by cooling. Another indirect relation to temperature is that if the bias voltage is kept constant, the change of the breakdown voltage will lead to a higher  $P_{tr}$  which is proportional to overvoltage  $V_{ov}$ .

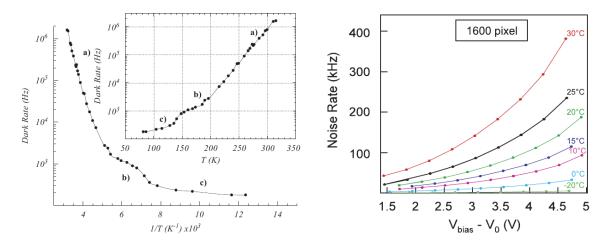

Figure 2.24 shows a dark rate meansurement of FBK-IRST SiPMs at different temperatures [62]. Trap assisted noise is found to be the dominant one at room temperature, marked as (a) in the Figure. Decreasing the temperature by 100 degrees will reduce the dark counts by three orders of magnitude. However, a further reduction of the temperature has a smaller influence on the noise as the tunnelling effect (marked (b)) then dominates the dark noise. At even lower temperature, the electrons starts to be frozen out so that a further decrease is observed (marked (c)). Similar results have also been obtained for Hamamatsu MPPCs [63].

Figure 2.25 shows a dark count measurement of a Hamamatsu MPPC  $1 \times 1 \text{mm}^2$  device at different overvoltage conditions. A linear relation is observed at low overvoltage values; this can be explained by the triggering probability  $P_{tr}$ , which is proportional to the overvoltage. At high voltages, afterpulsing and crosstalk start to take effect as their occurance probability is proportional to  $V_{av}^2$  [71].

Last but not least, the dark noise rate scales linearly with the detector area. This is because at room temperature the dominant trap assisted noise rate  $G_s$  is proportional to the number of trapping centers and the impurity density remains constant; this has been shown for SiPMs from e.g. STMicroelectronics, which are reported to have a perfect area scaling relation [72].

#### 2.3.4 After-pulse Effect

The after-pulse effect is another important noise source polluting output signals. It is related to the impurity centers inside the silicon wafer. Electrons and holes generated in the avalanche process will be

Fig. 2.24: SiPM dark rate vs. temperature [62]

Fig. 2.25: MPPC dark rate vs. overvoltage [2]

trapped by all the impurities (trapping centers) deep inside the forbidden band and then released later with a characteristic time constant. Since this time constant is relatively long compared to the avalanche time, the carrier is often released after the pixel has returned to its quiescent state. The released carrier might trigger a secondary avalanche called "after-pulse". The characteristic time constant is determined by the energy levels of the trapping centers within the gap; the after-pulse probability can be described by [73]:

$$P_{ap} = P_c \cdot \frac{exp - (t/\tau_a)}{\tau_a} \cdot P_{tr} \tag{2.21}$$

where  $P_c$  stands for the trap capture prabability;  $P_c$  is proportional to the carrier flux during the avalanche, the bias overvoltage  $V_{ov}$ ) as well as the impurity density.  $\tau_a$  is the trap lifetime, it depends totally on the trap energy level position.  $P_{tr}$  stands as before for the pixel triggering probability. Since the triggering probability also depends linearly on the bias overvoltage  $V_{ov}$ , the after-pulse probability  $P_{ap}$  is proportional to  $V_{ov}^2$ . Due to this special relation, after-pulsing can be suppressed by keeping the

Fig. 2.26: Pulse time interval for CPTA SiPMs [46] Fig. 2.27: T dependence of the trap lifetime [73]

reverse bias voltage after each breakdown shortly below the breakdown voltage using an active quench circuit. As a trade-off this can, however, increase the detector dead time.

The after-pulse release constant can be measured using standard waveform analysis. The time interval between two successive pulses can be used to analyze the afterpulse time constant. Figure 2.26 shows the result for CPTA SiPMs [3]. A fit using two exponentials can be used to describe the data, where the longer time constant corresponds to the poisson statistics of dark noise and the shorter one is the after-pulse time constant. It is quite clear from the plot that the after-pulse phenomenon happens during the first 500ns. In contrast, Hamamatsu MPPCs have a faster constant of about 15ns [74], for ST Microelectronics it is about 200ns [75] and for FBK-IRST one measures afterpulses within first 50ns [46]. Different values from different manufacturers imply that after-pulsing due to impurity is really sensitive to the detector structure and fabrication process.

It should be noted that the decay constant (trap lifetime) itself is also temperature dependent, i.e.  $\tau_a \propto exp(-E_A/kT)$  ( $E_A$  is the activation energy). Figure 2.27 displays results measured for different shallow junction SPADs [32]; the same behaviour has been confirmed by studies from Hamamatsu at cryogenic temperatures [63].

#### 2.3.5 Optical Crosstalk

Optical crosstalk is another unwanted side effect for Silicon Photomultipliers. Adjacent pixels are triggered due to the emission of optical photons during impact ionization. Figure 2.28 shows a picture of photon emission from SiPM samples produced by HLL München [76]. Red spots in the figure indicate suspicious pixels with substantial photon emission. The exact physical reason for the photon emission during the avalanche process is still under study. Possible explainations are recombination, bremsstrahlung and intraband transistions [77] or a combination of all these effects. Photon emission spectra from various devices differ significantly [78]. As a rule of thumb, Lacaita et al. estimated the photon emission probability to be about  $3 \times 10^{-5}$  per avalanche carrier [79].

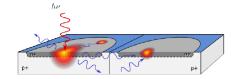

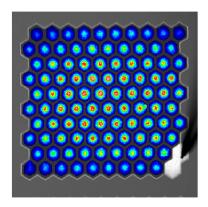

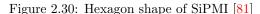

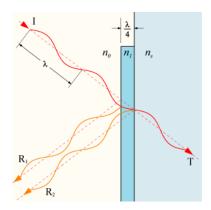

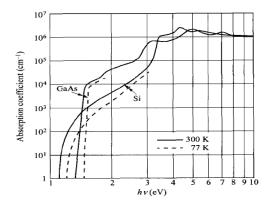

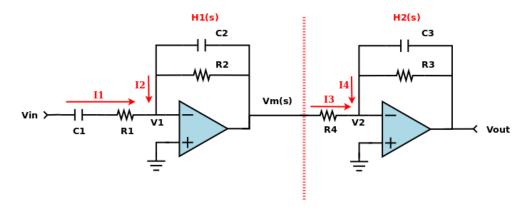

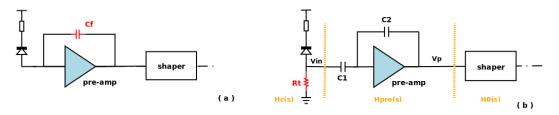

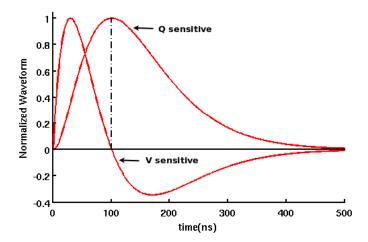

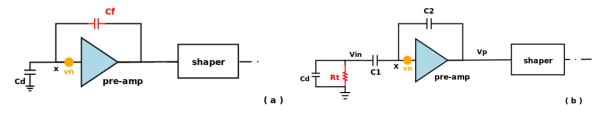

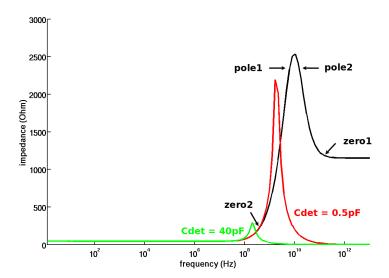

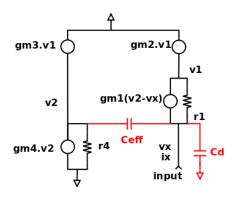

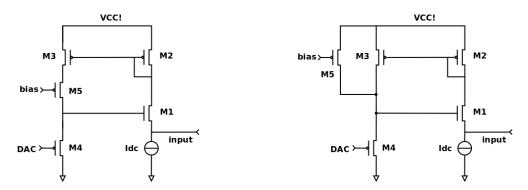

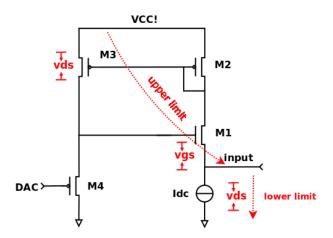

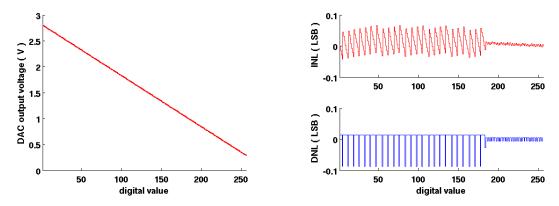

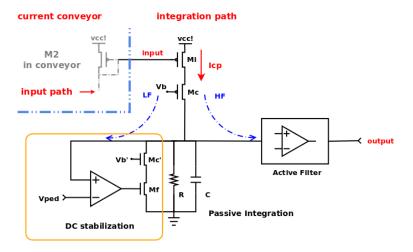

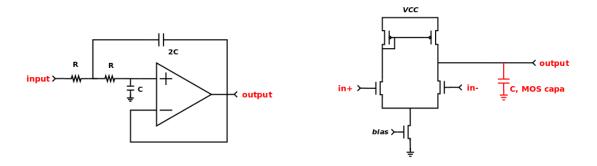

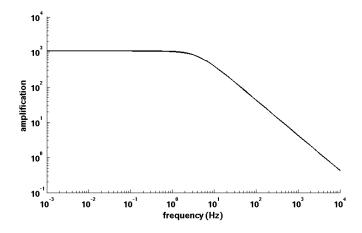

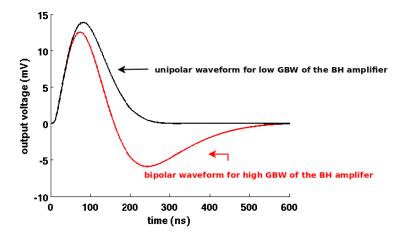

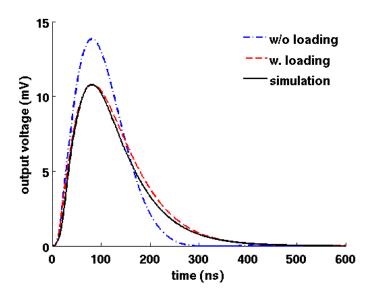

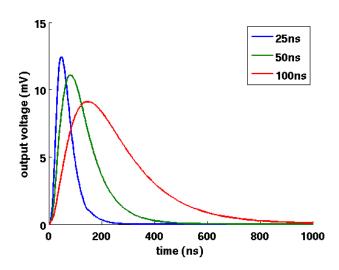

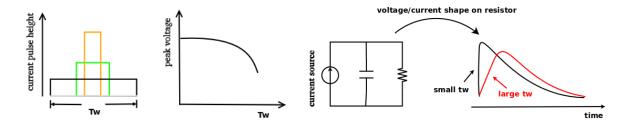

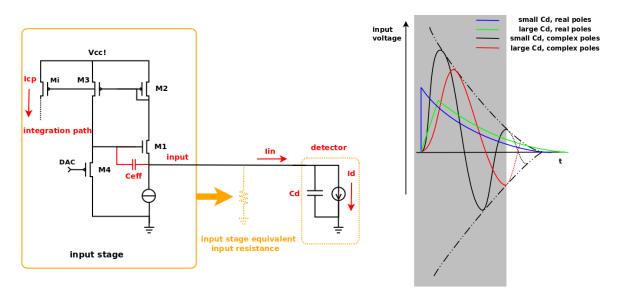

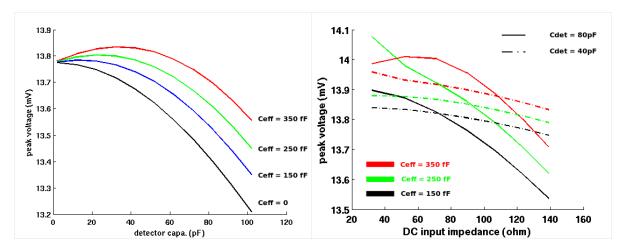

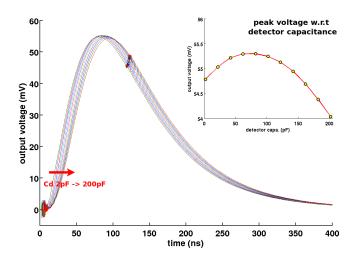

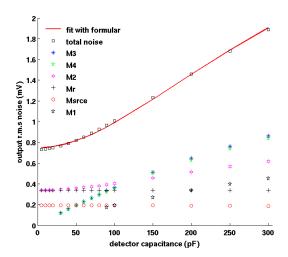

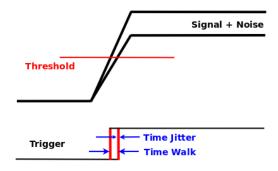

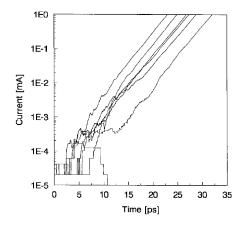

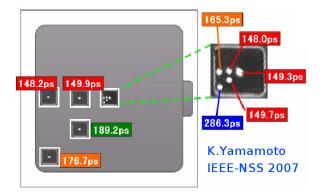

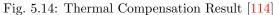

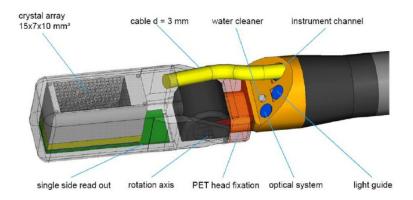

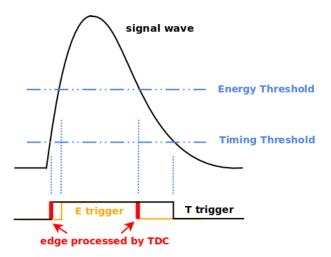

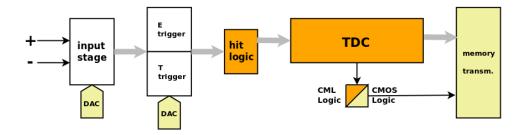

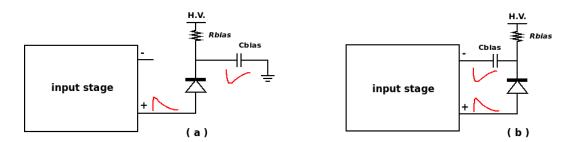

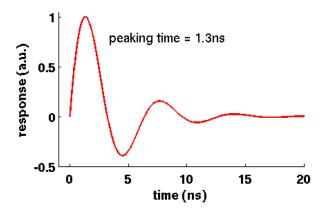

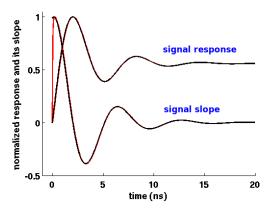

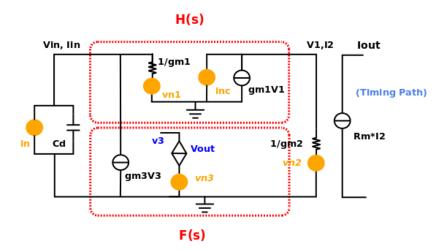

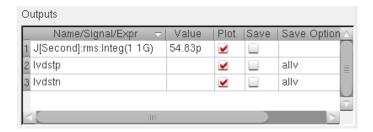

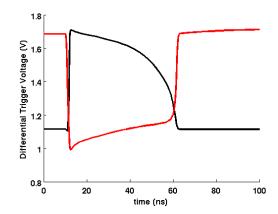

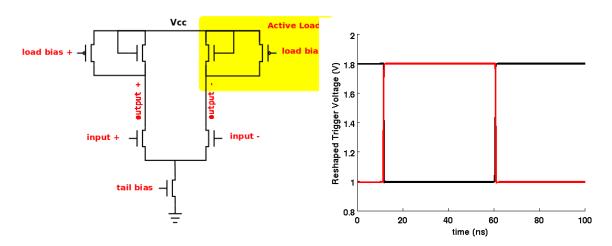

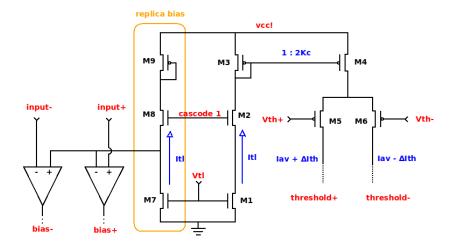

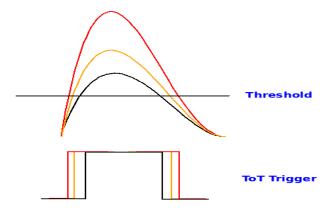

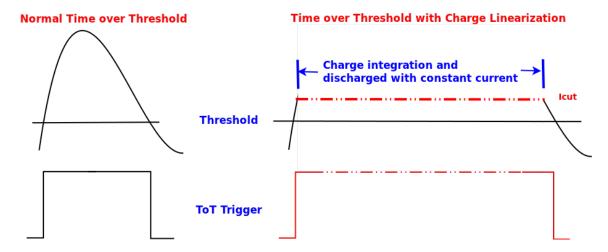

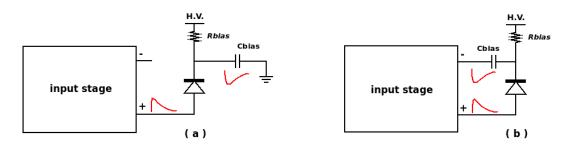

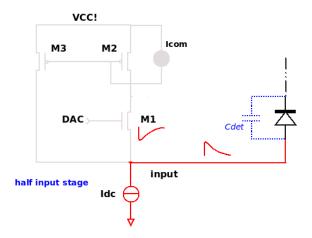

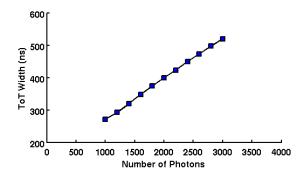

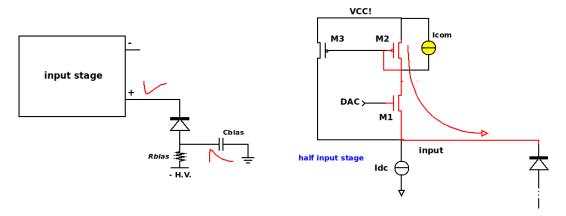

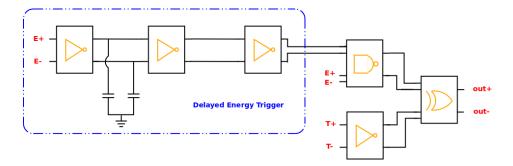

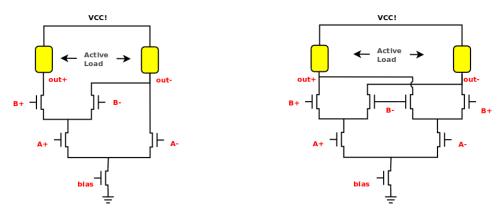

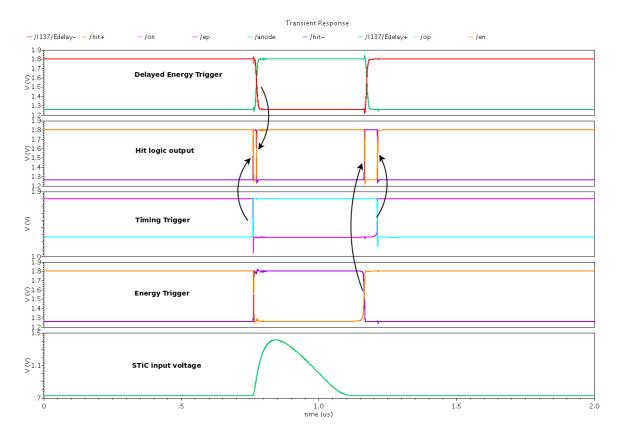

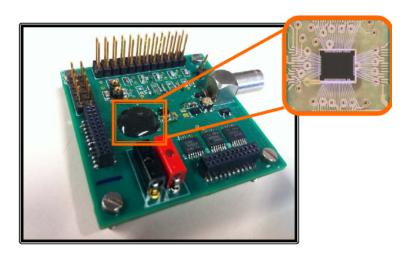

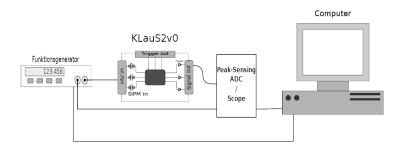

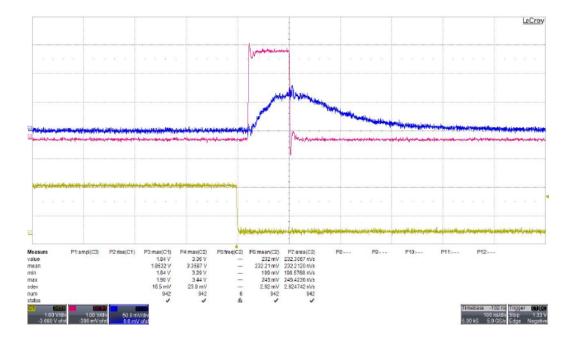

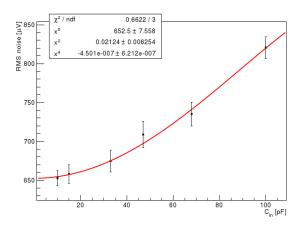

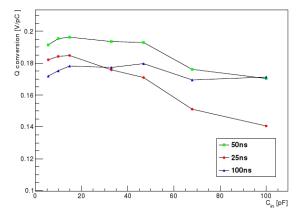

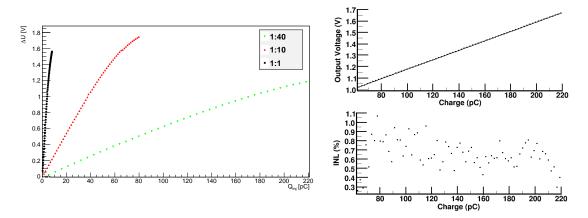

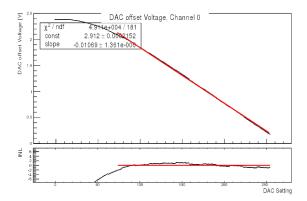

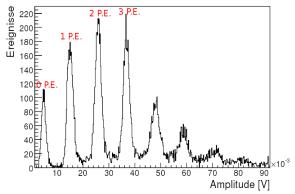

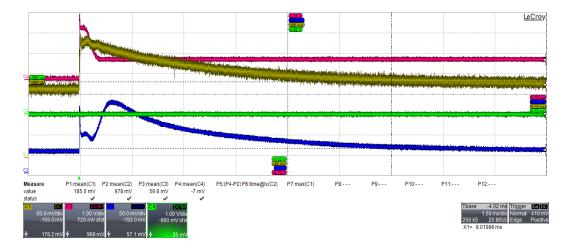

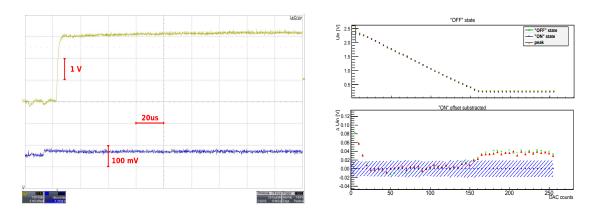

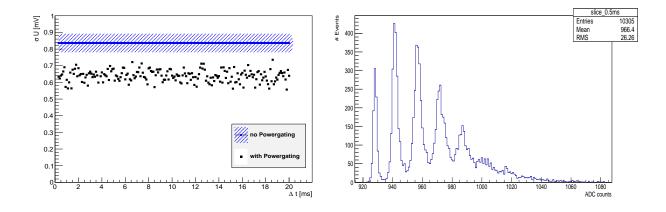

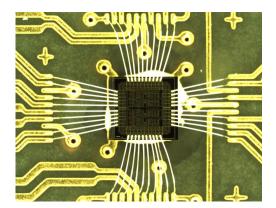

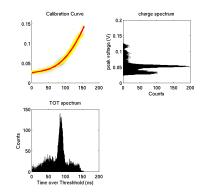

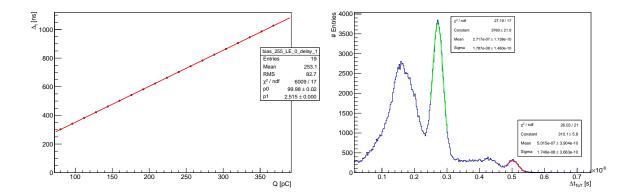

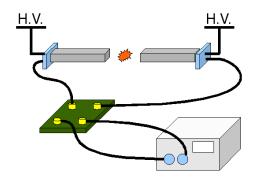

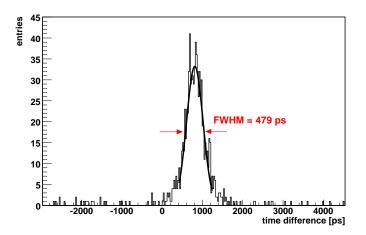

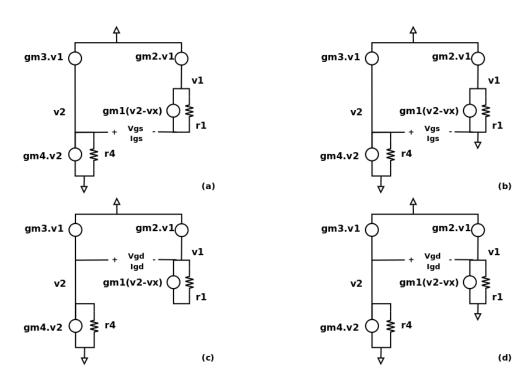

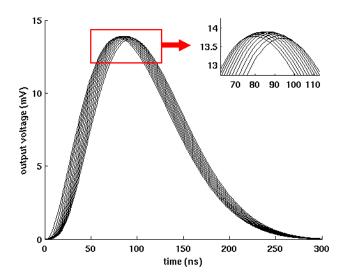

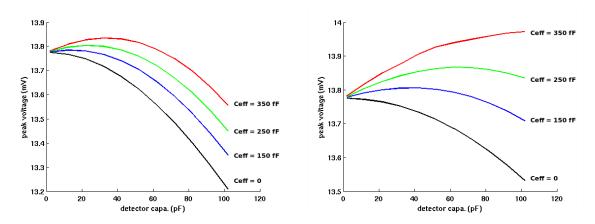

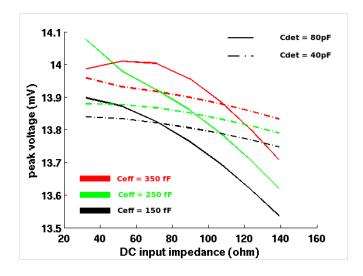

Since the photon is emitted during an avalanche, it still needs a coupling path to trigger neighbouring pixels. The photon can propagate either through a direct optical path or can be reflected via the silicon bulk as illustrated in Figure 2.29. The direct path can be decoupled by putting an opaque trench in between as shown in Figure 2.4. By doing this a prominent reduction of the crosstalk from 20% - 30% to 1% - 2% has been observed [18].